С логическими элементами разобрались, теперь на их основе можно делать целые устройства! Неплохо бы начать с триггеров. Триггеры - это такие устройства, которые позволяют хранить состояние. То есть по сути в триггер можно записать 0 или 1, чтобы потом их считать.

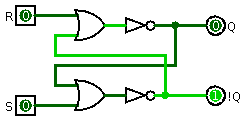

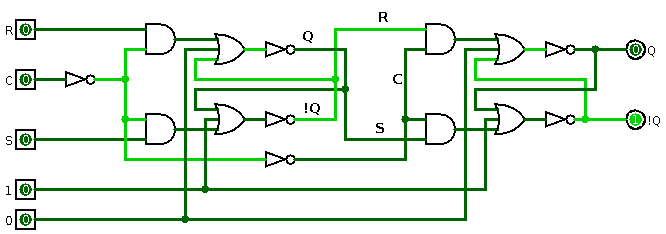

Триггер, который я буду дальше описывать, называется SR триггером. Такое название он получил за свои два входа: S (set) - записывает в триггер единицу, а R (reset) - записывает ноль. А ещё у него есть аж целых два выхода: прямой (Q) и инверсный (!Q). На прямой выход выводится значение ячейки, а на инверсный, соответственно названию, - инвертированное значение. Как по мне, хватило бы и одного выхода. Понятия не имею, зачем так сделано, может быть, дань традициям. Тем не менее, вот так можно собрать триггер из парочки элементов ИЛИ и парочки НЕ:

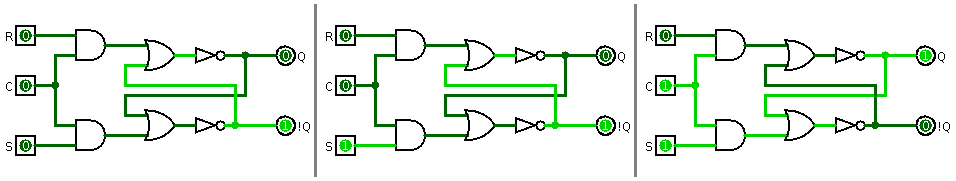

Эта конструкция примечательна тем, что в ней есть обратная связь. Значение с инвертированного выхода подаётся на вход в верхний эелемент ИЛИ и таким образом держит весь триггер в нулевом состоянии. Если теперь попробовать сбросить значение и подавать единицу на вход Reset, то ничего не поменяется. Но вот если подать единицу на вход Set, то триггер переключится в другое состояние. Пожалуй, лучше посмотреть, как элементы будут переключаться:

Итого получается, что, когда на вход ничего не подаётся, то триггер сохраняет своё состояние. А ещё его состояние можно устанавливать в единицу или сбрасывать в ноль. Казалось бы, и всё, но остался ещё один случай, доселе не рассмотренный, - подать единицу на оба входа! В таком случае оба элемента ИЛИ будут выдавать единицу. А оба элемента НЕ будут эту единицу конвертировать в ноль. И значит, на выходе и прямом, и инверсном будет тоже ноль. Вот, полюбуйтесь:

Выходит, что в ячейке сейчас записан ноль. Но и инвертированное значение тоже ноль. А хуже всего то, что если одновременно на оба входа теперь подать ноль, то непонятно, в каком состоянии будет после этого триггер. Поэтому такую ситуацию называют “Запрещённым состоянием”, и делать так нельзя. Это, конечно, не то же самое, что и короткое замыкание. То есть, ничего страшного, просто нельзя. Примерно как делить на ноль. Тоже ведь нельзя, но если уж не удержался и разделил, то ничего страшного. А ещё триггер принимает неопределённое состояние при включении, в случае, когда на всю плату подаётся питание. Так что после включения надо обязательно его сбросить перед использованием.

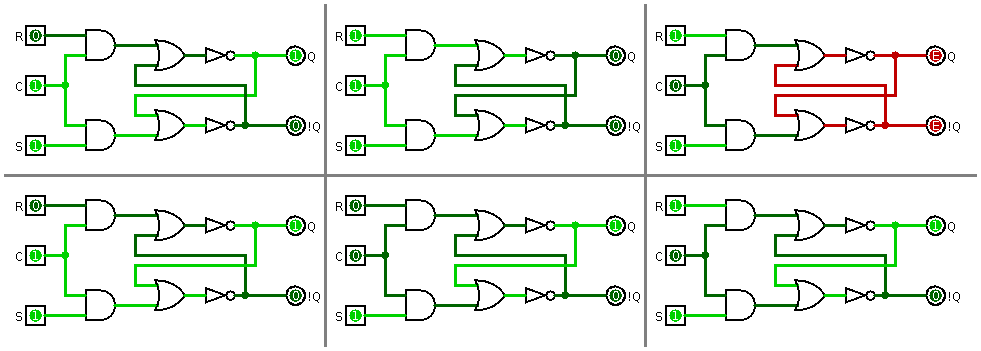

Приведенный выше триггер является асинхронным. Логично предположить, что бывают ещё и синхронные триггеры. В электронике (да и вообще много где) очень полезно, когда компоненты работают согласованно. Для схожих вещей, например, в оркестре ставят дирижёра. Он показывает начало тактов и таким образом синхронизирует всех музыкантов. Электрический аналог дирижёра - это тактовый генератор. Он вырабатывает ритм для синхронизирования электронных компонентов определённой частоты. Именно эту частоту можно увидеть в характеристиках процессора или материнской платы. Так вот синхронный триггер срабатывает под действием синхронизирующего сигнала. Для этих целей у него есть ещё один дополнительный вход C (от слова clock). Ниже располагается пример синхронного триггера, в котором записан ноль (слева). Потом подаётся сигнал на S для установки единицы, но ничего не происходит (посередине), пока не придёт синхроимпульс. И только с приходом синхронизирующего сигнала ячейка переключается в единицу (справа).

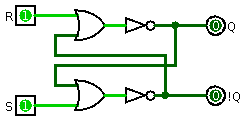

Уже неплохо, теперь, пока на тактовой линии держится ноль, триггер вообще никак не реагирует на SR входы. Зато вот когда от тактового генератора приходит единица, то ячейка ведёт себя, как асинхронная. Например, по какой-то причине сразу после установки единицы в триггере на вход R тоже приходит единица. И вот тут всё зависит от того, успеет ли тактовый генератор переключиться в ноль или нет. На иллюстрации ниже в первом случае генератор не успевает, и сигнал сброса приходит раньше. А во втором случае, сначала переключается тактовый сигнал, а уже потом приходит сброс.

Сверху получилось запрещённое состояние. Правда Logisim не будет показывать состояние E, а просто упадёт с ошибкой, эту ситуацию я руками нарисовал для наглядности.

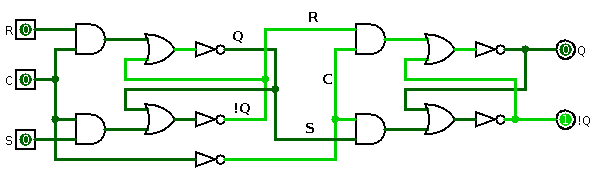

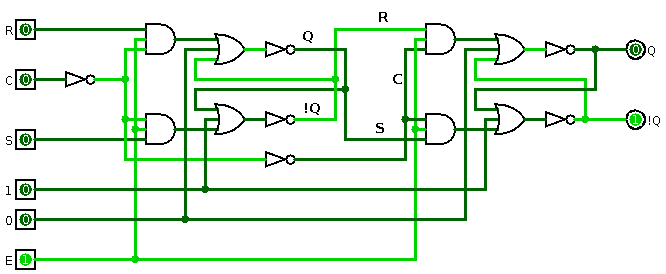

Есть случаи, когда такое срабатывание не годится. Тогда триггер должен менять свое состояние мгновенно во время перепада напряжения тактового сигнала. Для таких случаев собирают двухступенчатый триггер:

Тут просто две SR ячейки, стоящие друг за другом. Первая ячейка управляется от внешних входов, а вторая ячейка - от первой. Для этого прямой выход (Q) с первого триггера соединяем со входом S второго. Чтобы единица, записанная в первый триггер, также записывалась и во второй. Хитрость тут в том, что на первый триггер подаётся тактовый сигнал, как есть, а на второй - инвертированный. Таким образом, пока тактовый сигнал - единица, то, меняя S и R входы, можно менять состояние первого триггера. Но при этом второй триггер остаётся неизменным, и значение на выходе - тоже. А вот как только тактовый сигнал меняется, то тогда первый триггер остаётся, как есть, ведь для него теперь тактовый сигнал является нулём. Второй же триггер теперь включён и готов к изменениям, вот только на вход ему приходят данные от первого, который не изменяется. В общем, этот двухступенчатый триггер теперь меняет своё состояние только в случае, когда тактовый сигнал переходит из 1 в 0. Если надо, чтобы он переключался на переход из 0 в 1, то можно добавить ещё один инвертор на вход C:

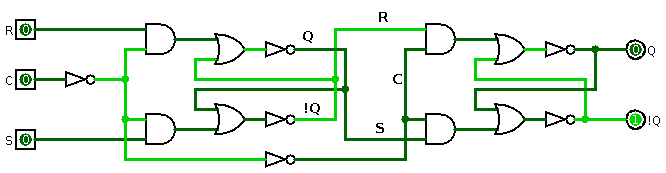

Не стоит забывать, что при подаче питания, то есть при первом включении, сложно предсказать, что же будет записано в триггере. И было бы неплохо иметь возможность просто и без хлопот сбросить значение триггера в 1 или 0 по желанию. Для таких вещей можно вывести ещё два дополнительных входа, асинхронных. Теперь в триггер можно записать 0 или 1, не дожидаясь синхроимпульса. У следующей версии триггера, помимо всего прочего, теперь есть ещё и асинхронные входы. И, как можно увидеть, - это просто S и R входы из асинхронной версии SR триггера.

Тут я заменил элементы ИЛИ с двумя входами, на трёхвходовые. Они работают точно так же: выдают единицу, если хотя бы на один вход приходит единица.

Но и на этом не обязательно останавливаться. Можно добавить ещё один вход - Enable (включить). Из названия очевидно, что, когда на вход “включить” подаётся сигнал, то триггер включается и начинает реагировать на синхронные входы. Кстати, при этом значение элемента подаётся на выходы всегда, вне зависимости от того, в каком состоянии Enable. То есть, если сначала в триггер записать единицу, а потом его выключить (подать в Enable ноль), то он всё равно будет выдавать единицу на выходе. Чтобы подвести сигнал включения, к каждому элементу И я добавил ещё один вход:

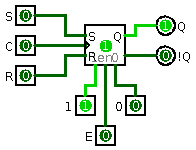

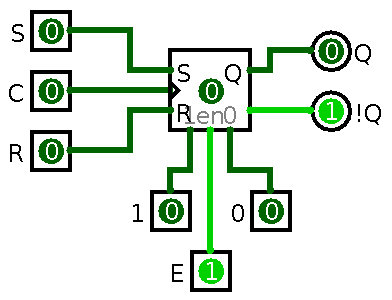

Ну вот и всё. Вот так вот можно собрать SR триггер из простейших логических элементов. В Logisim для обозначения этого триггера есть специальный элемент:

Я к нему подвёл входы и выходы для наглядности. Дело в том, что поначалу я не понимал, зачем внизу там подписано “1en0”. Оказалось, это просто 3 разных входа. Вдобавок, в середине элемента отображается его внутреннее состояние. Это очень удобно, чтобы быстро понять, что же в нём записано: